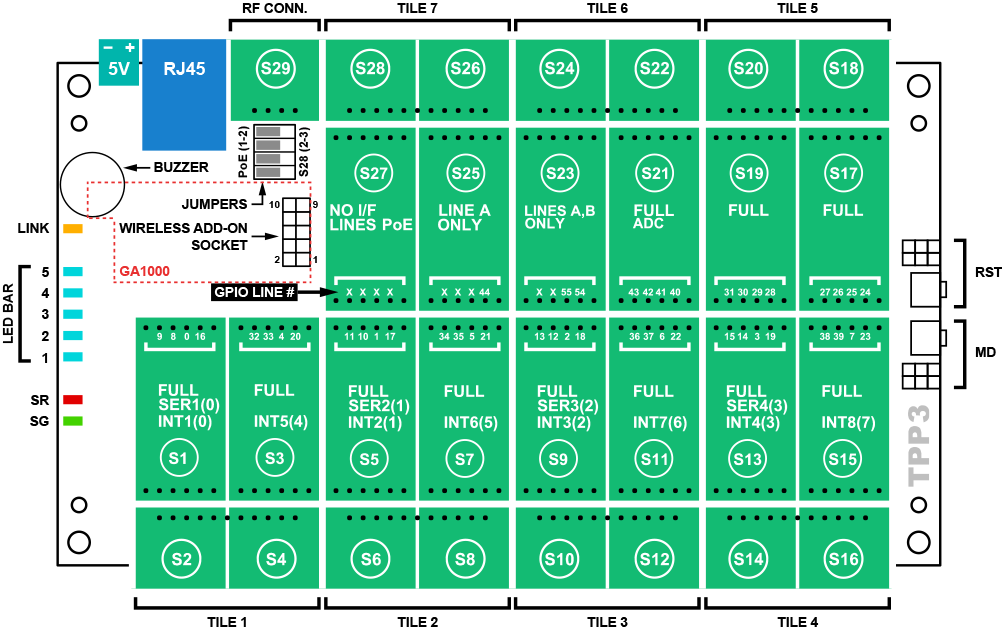

Tiles, Sockets, Connectors, Controls

The TPP3(G2) features 14 "M" and 14+1 "C" sockets.

Sockets (S1) ~ (S28) form seven standard tiles.

There are 47 control lines connecting "M" sockets to the CPU. The number of control lines is smaller than the number of "M" sockets multiplied by four. This is because some sockets have a reduced number of control lines, or have no lines connected at all:

- Socket (S23) only has control lines A and B. Control lines C and D are not implemented.

- Socket (S25) only has the control line A. Control lines B, C, and D are not implemented.

- Socket (S27) has no control lines connected to it.

- Remaining "M" sockets all have four control lines implemented.

Additionally:

- "M" sockets (S1), (S5), (S9), and (S13) have the UART capability.

- "M" sockets (S1), (S3), (S5), (S7), (S9), (S11), (S13), and (S15) have the interrupt capability.

- "M" socket (S21) has the ADC capability.

- "M" socket (S27) has the PoE capability, provided that four TPP3(G2) jumpers are set to 2-3 position (see below).

- "C" socket (S29) exists exclusively for the installation of RF connector Tibbit #37. This socket has no other functions.

Jumpers

Four jumpers next to the RJ45 jack define the connection between "M" socket (S27), "C" socket (S28), and the RJ45 jack:

- When the jumpers are in the 1-2 position, four power lines from the RJ45 jack are connected to four I/O lines of (S27). Under this arrangement, you can install an M1 PoE device into (S27), or M2 PoE device into (S25)-(S27).

- When the jumpers are in the 2-3 position, the RJ45 jack is disconnected from (S27), which is instead connected to (S28) in a "standard tile way."