#57, M1S: FPGA Tibbit

Function: Contains an ICE5LP1K-SWG36ITR50 FPGA from Lattice Semiconductor

Form factor: M1S

Category: Input/output module

Special needs: ---

Power requirements: 5V/25mA

See also: ---

Details

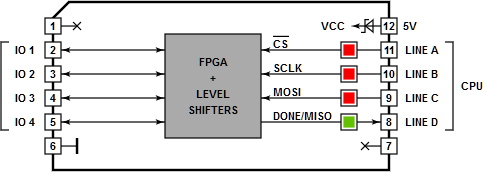

This Tibbit carries an ICE5LP1K-SWG36ITR50 FPGA from Lattice Semiconductor. The Tibbit is suitable for implementing a wide variety of configurations (functions). The list of currently available configurations is found in Implemented Configurations. Four I/O lines of the FPGA are exposed to the outside world. As the FPGA only works with 3.3V logical signals, there are automatic bi-directional level shifters between the FPGA and pins 2-5 of the Tibbit. "Automatic" means that these level shifters do not require direction control and choose the direction for each I/O line automatically, depending on which side (FPGA or an external circuit) is driving the line.

The Tibbit is controlled through the standard SPI lines: –CS, SCLK, MOSI, and MISO. There are two non-standard features built on top of the SPI functionality:

- The –CS and SCLK lines are used to produce a reset pulse for the FPGA IC.

- The MISO line also doubles as a status (DONE) line.

Both non-standard features are described in Resetting and Initializing the Onboard FPGA.

LEDs

There are three red LEDs and one green LED. These four LEDs are connected to the four interface lines of the Tibbit. The LEDs light up for the LOW state of their respective interface lines.

The red LEDs are connected to the –CS, SCLK, and MOSI lines. The green LED is connected to the DONE/MISO line.

Sample Project

The use of Tibbit #57 is illustrated by a Tibbo BASIC test project. You can find it here: https://github.com/tibbotech/CA-Test-Tibbit-57.

Further Info

Resetting and Initializing the Onboard FPGA