SSI Modes

The ssi.mode property defines one of the four possible modes for the CLK line. These modes directly correspond to the SPI modes as described here: http://en.wikipedia.org/wiki/Serial_peripheral_interface.

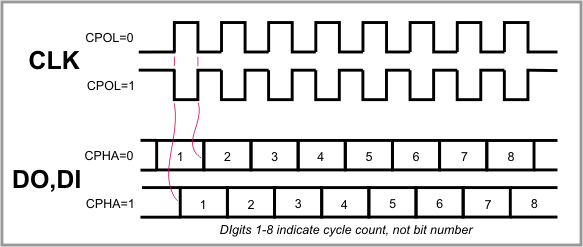

The SSI mode combines two independent parameters — CPOL (clock polarity) and CPHA (clock phase):

- Mode 0: CPOL = 0, CPHA = 0

- Mode 1: CPOL = 0, CPHA = 1

- Mode 2: CPOL = 1, CPHA = 0

- Mode 3: CPOL = 1, CPHA = 1

Here is a brief description of the modes — some "preparedness" is required to comprehend this:

- CPOL = 0: clock line is LOW when idle:

- CPHA = 0: data bits are captured on the CLK's rising edge (LOW-to-HIGH transition) and data bits are propagated on the CLK's falling edge (HIGH-to-LOW transition).

- CPHA = 1: data bits are captured on the CLK's falling edge and data bits are propagated on the CLK's rising edge.

- CPOL = 1: clock line is HIGH when idle:

- CPHA = 0: data bits are captured on the CLK's falling edge and data bits are propagated on the CLK's rising edge.

- CPHA = 1: data bits are captured on the CLK's rising edge and data bits are propagated on the CLK's falling edge.

Note that there is an additional difference:

- In SSI modes 1 and 3, the first data bit (in either direction) will be present on the DO (DI) line after the first transition on the CLK line.

- In SSI modes 0 and 2, the first data bit (in either direction) will be present on the DO (DI) line before transitions on the CLK line start.